|

приветствую создателей курса и благодарю за доступ к информации! понимаю, что это уже никто не исправит, но, возможно, будут следующие версии и было бы неплохо дать расшифровку сокращений имен регистров итд, дабы закрепить понимание их роли в общем процессе. |

Структура микропроцессорной системы

Назначение и функции чипсета в микропроцессорной системе

Чипсет (chIPset) - это набор БИС (обычно 1-3 микросхемы), функционально эквивалентный микросхемам, входящим в стандартную конфигурацию микропроцессорной системы.

Как правило, чипсет интегрирует в себе функции следующих устройств:

- контроллера оперативной памяти;

- контроллеров кэш-памяти 2-го и/или 3-го уровня;

- контроллеров ПДП;

- контроллеров приоритетных прерываний;

- контроллера клавиатуры;

- контроллера мыши PS/2 ;

- контроллера инфракрасного порта;

- таймера реального времени;

- моста шины PCI ;

- моста шины ISA и др.

Обычно в составе чипсета выделяют:

- северный мост (North Bridge) - системный контроллер, в который входит контроллер системной шины, шин AGP и PCI, ОЗУ и кэш-памяти (для наборов под обычный Pentium);

- южный мост (SOUTh Bridge) - периферийный контроллер, включающий контроллеры EIDE, клавиатуры, моста PCI-to-PCI, последовательных/параллельных портов, шины USB и других подобных устройств.

Выбор чипсета во многом определяет конфигурацию МПС и ее производительность. Если МП можно заменить, а емкость ОЗУ увеличить, то замена чипсета однозначно связана с заменой системной платы, а ограничения чипсета также однозначно ограничивают возможности замены других элементов МПС: МП, ОЗУ, внешних устройств.

Чипсет накладывает ограничения на следующие функциональные характеристики системы в целом: тип памяти, тип кэш-памяти второго и/или третьего уровня, тип МП, максимальная частота системной шины, тип шины PCI (32- или 64-разрядная); поддержка многопроцессорной конфигурации и некоторые другие характеристики.

Практика показывает, что разница в производительности системных плат разных фирм, построенных с применением одного и того же чипсета, составляет от силы несколько процентов, между тем как тот же параметр для различных чипсетов может отличаться на порядок.

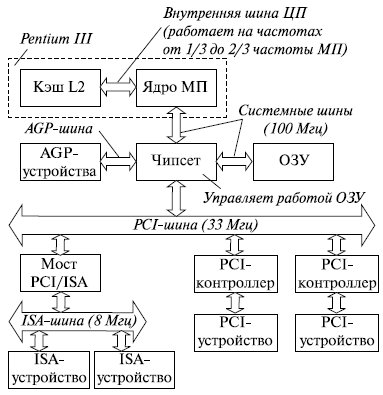

Рассмотрим использование чипсета на примере организации микропроцессорной системы на базе МП Pentium III на ядре Katmai (рис. 8.7).

Частота шины PCI составляет 33 МГц и при частоте системной шины и 66, и 100 МГц (используется деление частоты на 2 и 3 соответственно). AGP ( Accelerated GraphiCS Port ) - 32-разрядная шина (тактовая частота всегда 66 МГц), используемая для подключения графического адаптера и позволяющая ускорить обмен данными между графическим адаптером и основной памятью. В режиме AGP 2х эффективная частота в 133

МГц обеспечивается использованием обоих фронтов импульсов частоты 66 МГц. Шина ISA работает на частоте 8 МГц. За ее функционирование отвечает мост PCI/ISA, являющийся обычным PCI-устройством (просто встроенным в чипсет).

Системная шина может работать на разной частоте, но все эти варианты совместимы по разводке и электрически, что создает почву для "разгона".

Таким образом, при смене частоты системной шины, например, с 66 на 100 МГц замене подлежат лишь три устройства: процессор, чипсет и память. Никакие другие устройства не заметят подмены шины - ни AGPвидеоадаптеры, ни любой из PCI-контроллеров, ни старые ISA-карты. В этом и заключается принципиальное отличие шины 100 МГц от шины 66

МГц, разогнанной до 75/83 МГц. В первом случае новый чипсет обеспечивает работу PCI на частоте 33 (100/3) МГц, во втором старый чипсет и не подозревает о "разгоне" и продолжает делить частоту системной шины на 2, а в итоге частота PCI-шины равна 37,5 или 41,5 МГц, что может привести к неправильной работе некоторых PCI-устройств.

Краткие итоги. В лекции рассмотрены вопросы организации микропроцессорных систем, взаимодействия входящих в нее устройств. Подробно изложен режим прямого доступа в память и используемый, представлена структура контроллера ПДП. Описаны функции чипсета в микропроцессорной системе.