|

приветствую создателей курса и благодарю за доступ к информации! понимаю, что это уже никто не исправит, но, возможно, будут следующие версии и было бы неплохо дать расшифровку сокращений имен регистров итд, дабы закрепить понимание их роли в общем процессе. |

Структура микропроцессорной системы

Прямой доступ к памяти

В МПС используются два основных способа организации передачи данных между памятью и периферийными устройствами: программно управляемая передача и прямой доступ к памяти ПДП ( Direct Memory Access - DMA ).

Программно управляемая передача данных осуществляется при непосредственном участии и под управлением процессора. Например, при пересылке блока данных из внешнего устройства в оперативную память процессор должен выполнить следующую последовательность шагов:

- сформировать начальный адрес области обмена ОП;

- занести длину передаваемого массива данных в один из своих внутренних регистров, который будет играть роль счетчика;

- выдать команду чтения информации из ВУ; при этом на шину адреса из МП выдается адрес ВУ, на шину управления - сигнал чтения данных из ВУ, а считанные данные заносятся во внутренний регистр МП;

- выдать команду записи информации в ОП; при этом на шину адреса из МП выдается адрес ячейки оперативной памяти, на шину управления - сигнал записи данных в ОП, а на шину данных выставляются данные из регистра МП, в который они были помещены при чтении из ВУ;

- модифицировать регистр, содержащий адрес оперативной памяти;

- уменьшить счетчик длины массива на длину переданных данных;

- если переданы не все данные, то повторить шаги 3-6, в противном случае закончить обмен.

Как мы видим, программно управляемый обмен ведет к нерациональному использованию мощности микропроцессора, который вынужден выполнять большое количество относительно простых операций, приостанавливая работу над основной программой. При этом действия, связанные с обращением к оперативной памяти и к внешнему устройству, обычно требуют удлиненного цикла работы микропроцессора, что приводит к еще более существенным потерям производительности.

Альтернативой программно управляемому обмену служит прямой доступ к памяти - способ быстродействующего подключения внешнего устройства, при котором оно обращается к оперативной памяти, не прерывая работы процессора. Такой обмен происходит под управлением отдельного устройства - контроллера прямого доступа к памяти (КПДП).

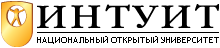

Схема включения КПДП в состав микропроцессорной системы представлена на рис. 8.4.

Перед началом работы контроллер ПДП необходимо инициализировать: занести начальный адрес области ОП, с которой производится обмен, и длину передаваемого массива данных. В дальнейшем по сигналу запроса прямого доступа контроллер фактически выполняет все те действия, которые обеспечивал микропроцессор при программно управляемой передаче.

Последовательность действий КПДП при запросе на прямой доступ к памяти со стороны внешнего устройства следующая:

- Принять запрос на ПДП (сигнал DRQ ) от ВУ.

- Сформировать запрос к МП на захват шин (сигнал HRQ ).

- Принять сигнал от МП ( HLDA ), подтверждающий факт перевода микропроцессором своих шин в третье состояние.

- Сформировать сигнал, сообщающий устройству ввода-вывода о начале выполнения циклов прямого доступа к памяти ( DACK ).

- Сформировать на шине адреса компьютера адрес ячейки памяти, предназначенной для обмена.

- Выработать сигналы, обеспечивающие управление обменом ( IOR, MW для передачи данных из ВУ в оперативную память и IOW, MR для передачи данных из оперативной памяти в ВУ).

- Уменьшить значение в счетчике данных на длину переданных данных.

- Проверить условие окончания сеанса прямого доступа (обнуление счетчика данных или снятие сигнала запроса на ПДП). Если условие окончания не выполнено, то изменить адрес в регистре текущего адреса на длину переданных данных и повторить шаги 5-8.

Прямой доступ к памяти позволяет осуществлять обмен данными между внешним устройством и оперативной памятью параллельно с выполнением процессором программы.

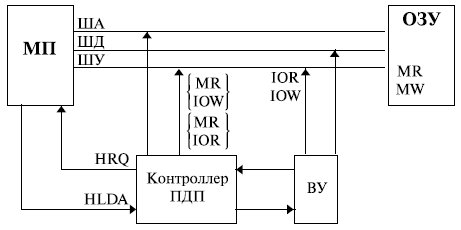

Структура КПДП представлена на рис. 8.5.

Контроллер состоит из 4 идентичных каналов, позволяющих подключить к системе до четырех устройств, работающих в режиме ПДП.

В состав каждого канала входят следующие регистры:

-

MR ( Mode Register ) - регистр режима. Определяет следующие параметры передачи:

- порядок изменения (увеличения или уменьшения) адреса ОП при передаче;

- возможность автоинициализации;

- режим обслуживания:

- одиночная передача (контроллер возвращает магистраль процессору после каждого цикла ПДП);

- блочная передача (контроллер владеет магистралью в течение передачи всего массива);

- по требованию (окончание передачи определяется снятием сигнала DRQ или подачей сигнала IEOP на внешний вход КПДП);

- каскадирование;

- CAR ( Current Address Register ) - регистр текущего адреса;

- BAR ( Base Address Register ) - базовый регистр адреса;

- CWR ( Current Word Register ) - текущий счетчик данных;

- WCR ( W0ord ConTRol Register ) - базовый счетчик данных.

Значения в регистрах BAR и WCR устанавливаются при инициализации и в ходе циклов ПДП не меняются. В регистры CAR и CWR в начале выполнения ПДП заносятся значения из регистров BAR и WCR соответственно. При выполнении ПДП эти регистры изменяются.

Управляющие регистры, общие для всего контроллера:

-

CR ( Command Register ) - регистр команд - определяет:

- режим память-память или обычный. В режиме память-память осуществляется обмен по схеме ПДП между двумя областями ОП (только для каналов 0 и 1) с использованием буферного регистра TR ( Temporary Register );

- запрет/разрешение ПДП;

- порядок изменения приоритетов каналов:

- фиксированный приоритет;

- циклическое изменение приоритета после обработки запроса на ПДП по одному из каналов;

- явное указание наиболее приоритетного канала;

- уровень сигналов DRQ и DACK (настройка на активный уровень сигналов под особенности работы внешних устройств);

- SR ( Status Register ) - регистр условий: используется для фиксации признаков обмена по каждому из каналов и программных запросов на ПДП.

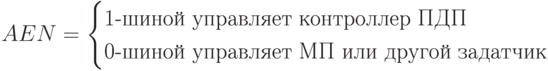

Во избежание ложных срабатываний внешних устройств, не использующих в данный момент режим прямого доступа, контроллер ПДП во время режима ПДП вырабатывает сигнал AEN, который блокирует работу остальных внешних устройств:

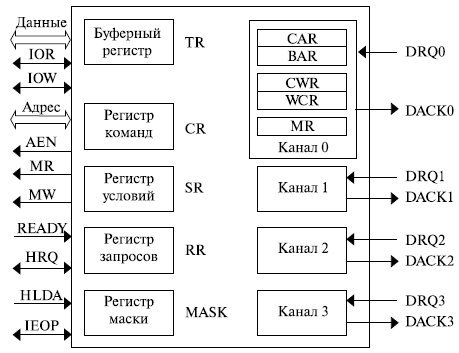

Для увеличения количества внешних устройств, которые могут быть подключены к микропроцессору в режиме ПДП, используется каскадное включение КПДП (рис. 8.6).

При этом ведомый КПДП подключается к одному из каналов ведущего контроллера по схеме подключения внешнего устройства, а непосредственно с микропроцессором связывается только ведущий контроллер. В стандартной конфигурации персональной ЭВМ применяются два КПДП (ведущий и ведомый), которые позволяют подключить до 7 внешних устройств, причем 2 канала закреплены за накопителями на жестком и гибком

дисках. В максимальной конфигурации при использовании ведущего и 4 ведомых КПДП, подключенных к каждому из каналов ведущего, к МП можно подключить до 16 внешних устройств, работающих в режиме ПДП.