Лекция 3: Образование групповых трактов высокого порядка. Плезиохронная цифровая иерархия

Преобразование в фиксированном режиме

Фиксированный режим (иногда его называют асинхронным) использует механизм вставки битов. Поток битов контейнера  непосредственно вставляется в информационные поля. Если потоки виртуальных контейнеров имеют различные скорости, то они мультиплексируются с помощью концепции согласование скоростей. Эта концепция разъясняется с помощью

рис.

3.11.

непосредственно вставляется в информационные поля. Если потоки виртуальных контейнеров имеют различные скорости, то они мультиплексируются с помощью концепции согласование скоростей. Эта концепция разъясняется с помощью

рис.

3.11.

Для упрощения понимания концепции выравнивания на

рис.

3.11 показан случай потоков с чередованием бит. Формат кадра выходного потока на этом рисунке имеет 10 бит, включая служебные биты. На вход поступают два входных потока. Канал 1 состоит из бит  ; канал 2 - из бит

; канал 2 - из бит  . Они объединяются в один поток по принципу чередования битов (см. обозначения каналов над выходным потоком).

. Они объединяются в один поток по принципу чередования битов (см. обозначения каналов над выходным потоком).

Для обеспечения выравнивания скоростей весь поток в этом примере разбивается на группы по 6 бит, по 3 от каждого входного потока. За этими битами (конец кадра) располагаются:

-

и

и  - биты, которые могут содержать следующие информационные биты потоков или биты выравнивания;

- биты, которые могут содержать следующие информационные биты потоков или биты выравнивания; -

и

и  - биты для управления выравниванием, указывающие тип данных в битах

- биты для управления выравниванием, указывающие тип данных в битах  и

и

- Например, если

то S1 - бит выравнивания, если

то S1 - бит выравнивания, если  , то

, то  - бит потока. Аналогичная логическая связь между указателем

- бит потока. Аналогичная логическая связь между указателем  и битом

и битом  .

.

Предположим, что из-за неточности генераторов входной поток канала 1 начинает опережать входной поток канала 2. Например, время поступления пятого бита первого канала (  ) начинает совпадать со временем поступления четвертого бита второго канала (

) начинает совпадать со временем поступления четвертого бита второго канала (  ).

).

После того как в  будет записан информационный бит

будет записан информационный бит  первого канала (значение

первого канала (значение  ), в

), в  записывается бит заполнения (

записывается бит заполнения (  ). Далее идет бит

). Далее идет бит  первого канала, (чередование бит каналов нарушается - это называют проскальзыванием). После чего мультиплексирование каналов идет в обычном режиме. Вставка одного бита из общего числа 7 позволяет скорректировать отклонения

первого канала, (чередование бит каналов нарушается - это называют проскальзыванием). После чего мультиплексирование каналов идет в обычном режиме. Вставка одного бита из общего числа 7 позволяет скорректировать отклонения  . Накопление существенного расхождения между потоками в реальных системах не такое обширное, поэтому вставка может производиться при большем числе переданных бит.

. Накопление существенного расхождения между потоками в реальных системах не такое обширное, поэтому вставка может производиться при большем числе переданных бит.

При демультиплексировании на приемном конце биты выравнивания удаляются.

Заметим один из недостатков систем с выравниванием. При одиночной ошибке в интерпретации бита вставки (например, интерпретация его как информационного бита) происходит потеря кадровой синхронизации.

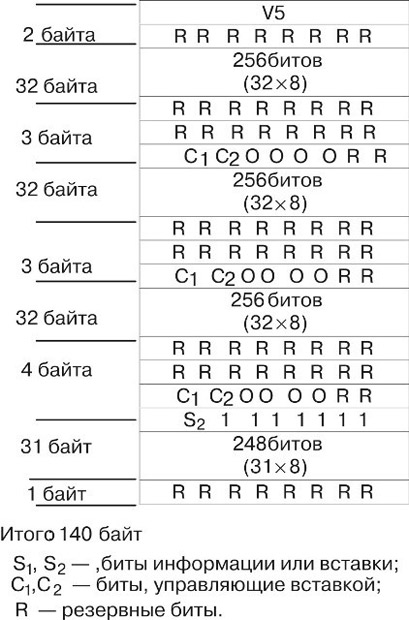

Структура поля полезной нагрузки одного виртуального контейнера при передаче сигналов потока  в терминальном блоке TU-12 в фиксированном режиме показана на

рис.

3.12.

в терминальном блоке TU-12 в фиксированном режиме показана на

рис.

3.12.

Число битов с фиксированной информацией

Группы трибных блоков (TUG-2, TUG-3)

Группы трибных блоков формируются с помощью трибных блоков нижнего уровня TU-2.

Блоки TUG-2 путем мультиплексирования трех блоков TU-12 переводятся в группу TUG-2, и далее группы блоков TUG-2 - в группу блоков TUG-3.

На рис. 3.13 показана процедура мультиплексирования блоков TUG-2 и TUG-3.

В результате мультиплексирования трех блоков TU-2 объемом 36 байт (4 столбца, 9 строк) получается одна группа блоков TUG-2 объемом 108 байт.

Дальнейшее мультиплексирование семи групп TUG-2 в группу TUG-3 дает группу блоков объемом 774 байта (  служебных столбца = 86 столбцов по 9 строк каждый), согласно схеме мультиплексирования PDH-трибов в технологии SDH по

рис.

3.13.

служебных столбца = 86 столбцов по 9 строк каждый), согласно схеме мультиплексирования PDH-трибов в технологии SDH по

рис.

3.13.

Перед переносом в контейнер  полученная информация в

полученная информация в  мультиплексируется (

мультиплексируется (  ) и образуется блок информации

) и образуется блок информации  байта.

байта.

Далее группа трибных блоков отображается в виртуальный контейнер  . Это отображение проводится, как это было показано ранее (

рис.

3.7): в виртуальный контейнер переносится полезная нагрузка нижнего уровня (

. Это отображение проводится, как это было показано ранее (

рис.

3.7): в виртуальный контейнер переносится полезная нагрузка нижнего уровня (  ) и вставляется обычный для виртуального контейнера заголовок. Таким образом, объем нагрузки виртуального контейнера составляет:

) и вставляется обычный для виртуального контейнера заголовок. Таким образом, объем нагрузки виртуального контейнера составляет:

- нагрузка трех

- нагрузка трех  ;

;

9 байтов - маршрутный заголовок.

Итого  , что составляет

, что составляет  столбцов. Для получения полного поля, составляющего

столбцов. Для получения полного поля, составляющего  , добавляются

, добавляются  столбца по

столбца по  байтов каждый. Поэтому полный объем информации виртуального контейнера

байтов каждый. Поэтому полный объем информации виртуального контейнера  равен

равен  столбцу или

столбцу или  байт.

байт.

Для получения модуля  следует добавить указатели административного блока (для получения блока

следует добавить указатели административного блока (для получения блока  ) и транспортный заголовок - для получения

) и транспортный заголовок - для получения  . Таким образом, получен модуль

. Таким образом, получен модуль  в виде кадра

в виде кадра  байтов, что, как было показано, при частоте 8000 байт в секунду составляет скорость передачи 155,52 Мбит/c.

байтов, что, как было показано, при частоте 8000 байт в секунду составляет скорость передачи 155,52 Мбит/c.