|

Добрый день!

Скажите, пожалуйста,планируется ли продолжение курсов по нанотехнологиям? Спасибо, Евгений

|

Термальный синтез микропрограмм алгоритмически ориентированных МКМД-бит-потоковых субпроцессоров

5.2. Термальный синтез DD-ассоциативных вычислительных конструкций алгоритмически ориентированного субпроцессора подстановки данных

Чтобы перейти от интерактивного к формализованному синтезу микропрограмм МКМД-бит-потоковых субпроцессоров, прежде всего необходимо формализовать синтез библиотечных слов- и поток-инструкций, а также процедур их компоновки на бит-матрице и редак-

тирования пространственно-временных FIFO -регистровых связей между операционными модулями, где локальный фазовый сдвиг даже на 1 такт приводит к потере работоспособности всего субпроцессорного тракта. Именно последнее обстоятельство делает сходными проблемы фазирования в МКМД-бит-потоковых технологиях с проблемами (де)когерентиза-ции в супрамолекулярных, наноэлектронных и квантовых вычислителях (см. раздел 7.3 [94]).

Как показал опыт, для успешной формализации процедур синтеза библиотечных слов-инструкций в МКМД-бит-потоковых технологиях требуется промежуточный (термальный) уровень декомпозиции функций, в "терминах" которого описывается рекуррентный алгоритм работы соответствующего операционного модуля, топологическая схема которого в основном определяется разрядностью  и размерностью циклически преобразуемых операндов

и размерностью циклически преобразуемых операндов  .

.

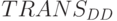

Методику термального синтеза микропрограмм слов- и поток-инструкций в полной мере иллюстрируют рекуррентные процедуры построения операционных модулей поток-инструкции перестановки данных ( TRANS ) по верхнему индексу  , которые гарантированно удовлетворяют системообразующее для МКМД-бит-потоковых технологий неравенство (6.1) курса "Задачи и модели вычислительных наноструктур", если используются в большом количестве циклов

, которые гарантированно удовлетворяют системообразующее для МКМД-бит-потоковых технологий неравенство (6.1) курса "Задачи и модели вычислительных наноструктур", если используются в большом количестве циклов  . При этом возможны два случая, когда синтезированный поток-оператор покрывает все факториальное пространство подстановок

. При этом возможны два случая, когда синтезированный поток-оператор покрывает все факториальное пространство подстановок  :

:

-

без изменения топологии микропрограммы, то есть только за счет вариаций порядка следования псевдослучайных адресов

что характерно для классических DD-ассоциативных конструкций;

что характерно для классических DD-ассоциативных конструкций; - с изменением топологии микропрограммы в зависимости от содержимого потока адресов

и/или преобразуемого потока данных

и/или преобразуемого потока данных  что характерно для PD-ассоциативных конструкций.

что характерно для PD-ассоциативных конструкций.

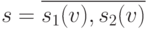

Здесь  ;

;  ;

;

!, и в каждом

!, и в каждом  -м цикле выполняемая подстановка

-м цикле выполняемая подстановка  может изменяться, сохраняя свои параметры

может изменяться, сохраняя свои параметры  ;

;  . Сокращенная формальная запись

. Сокращенная формальная запись  -й подстанов-ки содержит только множество транспозиций:

-й подстанов-ки содержит только множество транспозиций:  , где

, где  и

и  .

.

Учитывая, что любая конечная группа изоморфна некоторой (под)груп-пе подстановок, такой субпроцессор можно считать теоретико-групповым [103], если поток-оператор TRANS дополнить системными средствами поиска по заданной группе изоморфной ей подгруппы подстановок.

В традиционной вычислительной технике для выполнения подстановок обычно используют ЗУПВ в одном из двух режимов:

- запись потока входных данных в ячейки памяти

в порядке их

поступления, то есть по индексу

в порядке их

поступления, то есть по индексу  , где

, где  , и чтение ячеек

памяти в порядке подстановки, то есть по индексу

, и чтение ячеек

памяти в порядке подстановки, то есть по индексу  ;

; - запись потока входных данных в ячейки памяти в порядке подстановки:

и чтение ячеек памяти в хронологическом порядке по

и чтение ячеек памяти в хронологическом порядке по  .

.

С системотехнических позиций оба режима эквивалентны, так как требуют одних и тех же объемов памяти -  бит, и используют ЗУПВ с разделением времени между фазами записи и чтения. В результате цикл выполнения подстановки оказывается равным

бит, и используют ЗУПВ с разделением времени между фазами записи и чтения. В результате цикл выполнения подстановки оказывается равным  , что снижает в 2 раза регламентируемый теоремой Котельникова предельный темп поступления и обработки сигналов и изображений. Чтобы компенсировать такие временные издержки, используют парафазную схему включения двух блоков ЗУПВ, что позволяет совместить во времени фазу записи

, что снижает в 2 раза регламентируемый теоремой Котельникова предельный темп поступления и обработки сигналов и изображений. Чтобы компенсировать такие временные издержки, используют парафазную схему включения двух блоков ЗУПВ, что позволяет совместить во времени фазу записи  -й подстановки в одном блоке, с фазой чтения

-й подстановки в одном блоке, с фазой чтения  -й подстановки в другом блоке. В результате в 2 раза возрастает объем используемой ЗУПВ, но "средний" цикл выполнения одной подстановки становится равным S.

-й подстановки в другом блоке. В результате в 2 раза возрастает объем используемой ЗУПВ, но "средний" цикл выполнения одной подстановки становится равным S.

В операционном модуле МКМД-бит-потоковой инструкции  используется не ЗУПВ, а

используется не ЗУПВ, а

-битных FIFO -регистров, причем каждая, в том числе и "тождественная транспозиция"

-битных FIFO -регистров, причем каждая, в том числе и "тождественная транспозиция"  -й подстановки выполняется линейной последовательностью из 3 слов-инструкций:

-й подстановки выполняется линейной последовательностью из 3 слов-инструкций:

- дешифрации адреса -

,

, - записи и хранения -

,

, - чтения -

.

.

Ограничим рассмотрение различных вариантов реализации МКМД-бит-потоковой инструкции  и вторым режимом работы FIFO -регистровой памяти, считая, что индекс подстановки

и вторым режимом работы FIFO -регистровой памяти, считая, что индекс подстановки  меняется с максимально возможной скоростью, то есть на каждом

меняется с максимально возможной скоростью, то есть на каждом  -м цикле использования поток-оператора, и поэтому

-м цикле использования поток-оператора, и поэтому  .

.

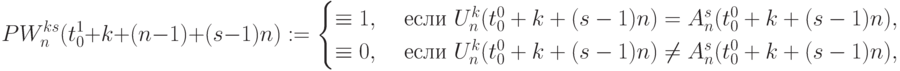

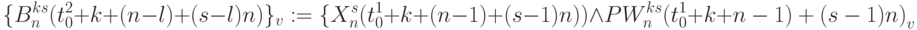

В DD -ассоциативной векторно-конвейерной поток-инструкции  снимается ограничение на

снимается ограничение на  и каждая из

и каждая из  "транспозиций", входящих в

"транспозиций", входящих в  -ю подстановку, выполняется линейной последовательностью слов-инструкций:

-ю подстановку, выполняется линейной последовательностью слов-инструкций:

-

Дешифратор адреса

-й "транспозиции"

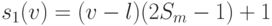

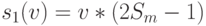

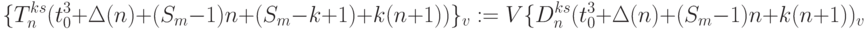

-й "транспозиции"  представляет собой строку матрицы (терм) из 7 бит-процессоров (рис. 5.3), на выходе каналов АЛУ которой реализуется преобразование:

представляет собой строку матрицы (терм) из 7 бит-процессоров (рис. 5.3), на выходе каналов АЛУ которой реализуется преобразование:

( 5.1) где все аргументы и параметры целочисленные:

-

- подстановочный адрес

- подстановочный адрес

-й "транспозиции";

-й "транспозиции";

-

- натуральный ряд чисел, задающих номера строк бит-матрицы или, что одно и то же, пространственные адреса кольцевых FIFO -регистров

- натуральный ряд чисел, задающих номера строк бит-матрицы или, что одно и то же, пространственные адреса кольцевых FIFO -регистров  , которые заносятся со сдвигом влево и циклически воспроизводятся на выходах бит-инструкций

, которые заносятся со сдвигом влево и циклически воспроизводятся на выходах бит-инструкций  первого столбца матрицы;

первого столбца матрицы; -

- начальная задержка потоков псевдослучайных адресов

- начальная задержка потоков псевдослучайных адресов  и преобразуемых потоков данных

и преобразуемых потоков данных  , которая может появиться во входном интерфейсе субпроцессора

, которая может появиться во входном интерфейсе субпроцессора  при компоновке слов-инструкций на бит-матрице (в библиотечном модуле

при компоновке слов-инструкций на бит-матрице (в библиотечном модуле  );

); -

- суммарная "технологическая" задержка на выходе

- суммарная "технологическая" задержка на выходе  -й слов-инструкции

-й слов-инструкции  , где

, где  включает: 1 такт - на

включает: 1 такт - на  , 3 такта - на

, 3 такта - на  (монтажное "ИЛИ"), 1 такт - на

(монтажное "ИЛИ"), 1 такт - на  и 2 такта - на

и 2 такта - на  , из которых только в

, из которых только в  задержка зависит от

задержка зависит от  (в данном случае

(в данном случае  бит и

бит и  тактов);

тактов); -

- "технологическая" задержка на распространение

- "технологическая" задержка на распространение  и

и  по каналам транзита соответственно до входа и выхо-да

по каналам транзита соответственно до входа и выхо-да  -й слов-инструкции

-й слов-инструкции  , то есть

, то есть  -й строки бит-матрицы рис. 5.3;

-й строки бит-матрицы рис. 5.3; -

- функциональная задержка в каждой

- функциональная задержка в каждой  -й слов-инструкции

-й слов-инструкции  , которая расходуется на размещение признака результата в старший (

, которая расходуется на размещение признака результата в старший (  -й) бит каждого

-й) бит каждого  -го цикла сравнения;

-го цикла сравнения; -

- фазовый сдвиг

- фазовый сдвиг  и

и  соответственно в бит-потоках данных

соответственно в бит-потоках данных  и

и  , где

, где  и

и  ;

; -

- хронологический адрес синхронного поступления

- хронологический адрес синхронного поступления  и

и  на соответствующие входы

на соответствующие входы  ;

; -

- период активности поток-инструкции

- период активности поток-инструкции  на

на  циклах ее использования, так как по условиям правильной

работы требуется, чтобы в потоке данных

циклах ее использования, так как по условиям правильной

работы требуется, чтобы в потоке данных  и псевдослучайных адресов

и псевдослучайных адресов  только первые

только первые

-битных слов были значащими, а остальные

-битных слов были значащими, а остальные  слов - "нулевыми".

слов - "нулевыми".

Главная особенность слов-инструкции

состоит в потоковой реализации схемы "ИЛИ" с

состоит в потоковой реализации схемы "ИЛИ" с  входами (бит-процессоры 3-5 столбцов рис. 5.3), где результат циклического сравнения пространственного и потокового адресов (бит-процессоры 2-го столбца матрицы) размещаются в 8-м бите каждого

входами (бит-процессоры 3-5 столбцов рис. 5.3), где результат циклического сравнения пространственного и потокового адресов (бит-процессоры 2-го столбца матрицы) размещаются в 8-м бите каждого  -го цикла. В дальнейшем содержимое этого бита циклически выделяется в бит-процессорах 7-го столбца матрицы, где и формируется

-го цикла. В дальнейшем содержимое этого бита циклически выделяется в бит-процессорах 7-го столбца матрицы, где и формируется  -битный результат дешифрации

-битный результат дешифрации  .

. -

-

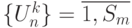

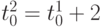

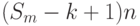

Блок записи и хранения содержимого

состоит из

состоит из  термов в виде кольцевых FIFO -регистров

термов в виде кольцевых FIFO -регистров  (строка бит-матрицы рис. 5.4), на каждом входе которого (бит-процессоры 2-го столбца) реализуется преобразование:

(строка бит-матрицы рис. 5.4), на каждом входе которого (бит-процессоры 2-го столбца) реализуется преобразование:

( 5.2) где:

-

- суммарная "технологическая" задержка

- суммарная "технологическая" задержка  до

выхода

до

выхода  -й слов-инструкции

-й слов-инструкции  , входящей в

, входящей в  (для

(для  бит

бит  тактов);

тактов); -

,

,  и

и  - соответственно начальное и конечное значение хронологического индекса

- соответственно начальное и конечное значение хронологического индекса  на

на  -м цикле использования

-м цикле использования  ;

; -

- фактический цикл записи всего потока

- фактический цикл записи всего потока  в

в  в

в  -м цикле использования поток-инструкции

-м цикле использования поток-инструкции  .

.

Циклическое (по

) хранение

) хранение  в

в  кольцевых FIFO -регистрах

кольцевых FIFO -регистрах  на

на  -м цикле их использования (выходы бит-процессоров 4-го столбца рис. 5.4) имеет вид:

-м цикле их использования (выходы бит-процессоров 4-го столбца рис. 5.4) имеет вид:

( 5.3) где:

-

- определяется той частью кольцевого циклического FIFO -регистра, которая заключена между его входом и схемой "И", обеспечивающей обнуление его содержимого с циклом

- определяется той частью кольцевого циклического FIFO -регистра, которая заключена между его входом и схемой "И", обеспечивающей обнуление его содержимого с циклом  тактов и период хранения

тактов и период хранения  в

в  , равный

, равный  тактов (для

тактов (для  бит

бит  тактам);

тактам);

-

- поток "обнуляющих" операндов, который поступает на вход RS и который имеет циклический по

- поток "обнуляющих" операндов, который поступает на вход RS и который имеет циклический по  вид

вид  и

и  для всех

для всех  .

.

-

-

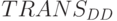

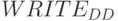

Блок чтения

содержимого

содержимого  кольцевых FIFO -регистров

кольцевых FIFO -регистров  (термов) на

(термов) на  -м цикле их использования (входы бит-процессоров 1-го столбца рис. 5.5 или, что одно и то же, выходы бит-процессоров 5-го столбца рис. 5.4) реализует преобразование:

-м цикле их использования (входы бит-процессоров 1-го столбца рис. 5.5 или, что одно и то же, выходы бит-процессоров 5-го столбца рис. 5.4) реализует преобразование:

( 5.4) где:

-

- суммарная "технологическая" задержка

- суммарная "технологическая" задержка  до выхода слов-инструкции

до выхода слов-инструкции  (для

(для  бит

бит  тактов);

тактов); -

- сдвиг разделенных во времени фаз записи и чтения, а

- сдвиг разделенных во времени фаз записи и чтения, а  ;

; -

- поток управляющих операндов, который формирует-ся бит-процессорами 2-го и 3-го столбцов рис. 5.5, распространяется по строкам бит-матрицы с задержкой

- поток управляющих операндов, который формирует-ся бит-процессорами 2-го и 3-го столбцов рис. 5.5, распространяется по строкам бит-матрицы с задержкой  и имеет циклический по

и имеет циклический по  вид

вид  и

и  для всех

для всех  ;

; -

- циклическая по

- циклическая по  константа, которая задает однократный цикл "записи-чтения", равный

константа, которая задает однократный цикл "записи-чтения", равный  тактов, и которая имеет вид: 1-й бит - "единица" и остальные биты - "нули";

тактов, и которая имеет вид: 1-й бит - "единица" и остальные биты - "нули"; -

- циклическая по

- циклическая по  константа, которая задает разрядность обрабатываемых операндов и которая имеет вид: 1-й бит - "единица", а остальные

константа, которая задает разрядность обрабатываемых операндов и которая имеет вид: 1-й бит - "единица", а остальные  бит - "нули".

бит - "нули".

-

-

Встроенный в

блок

блок  вывода данных

вывода данных  через

через  -битный FIFO -порт, на выходе которого (выход вертикального канала транзита бит-процессоров 1-го столбца рис. 5.5) реализуется преобразование:

-битный FIFO -порт, на выходе которого (выход вертикального канала транзита бит-процессоров 1-го столбца рис. 5.5) реализуется преобразование:

( 5.5) где:

- "технологическая" задержка на распространение

- "технологическая" задержка на распространение  от

от  -го входа и до выхода схемы "ИЛИ" с

-го входа и до выхода схемы "ИЛИ" с  входами FIFO -регистрового порта вывода.

входами FIFO -регистрового порта вывода.

Из приведенных данных видно, что в соотношениях (5.1)-(5.3) в качестве хронологического используется индекс  , а в соотношениях (5.4)-(5.5) в этом качестве выступает индекс

, а в соотношениях (5.4)-(5.5) в этом качестве выступает индекс  .

.