Междисциплинарный характер компьютерных проектов

1.5. Интенсивные и экстенсивные факторы повышения пропускной способности вычислительных систем по потокам команд и данных

Главным стимулом развития средств вычислительной техники является постоянное отставание на 2-3 порядка предоставляемой производительности (  ) от требуемой, первая из которых определяется уровнем технологии производства элементной базы и аппаратуры, а вторая диктуется задачами пользователя. Лидерами по предъявляемым требованиям к производительности являются задачи, решаемые в реальном времени, темп которого задается теоремой Котельникова:

) от требуемой, первая из которых определяется уровнем технологии производства элементной базы и аппаратуры, а вторая диктуется задачами пользователя. Лидерами по предъявляемым требованиям к производительности являются задачи, решаемые в реальном времени, темп которого задается теоремой Котельникова:

где  - максимальная частота в спектре обрабатываемого сигнала,

а

- максимальная частота в спектре обрабатываемого сигнала,

а  - период дискретизации сигнала по Котельникову.

- период дискретизации сигнала по Котельникову.

К таким задачам по-прежнему относятся задачи военного назначения:

- задачи управления фазированными антенными решетками произвольной аэродинамической формы, для решения которых уже сейчас необходимы вычислительные комплексы с производительностью порядка 1012 операций/сек;

- задачи всепогодной аэрокосмической разведки подвижных наземных группировок, для решения которых уже сейчас необходимы вычислительные комплексы с производительностью порядка 1015 операций/сек;

- задачи прецизионного определения положения на местности высокоманевренного летательного аппарата, для решения которых уже сейчас необходимы вычислительные комплексы с производительностью порядка 1010 операций/сек, и т. д.

Удовлетворить требования задач с экстремальными характеристиками по производительности можно двумя взаимодополняющими путями:

- технологическим, когда совершенствование производства элементной базы и аппаратуры приводит к росту тактовой частоты и снижению массо-габаритов и потребляемой ВС энергии;

- архитектурным, когда вычисления распараллеливаются, что приводит к росту массо-габаритов и потребляемой энергии, а также к росту системных аппаратно-временных затрат на управление вычислительным процессом в (сверх)многопроцессорных БВС или ее компонентах.

Прирост производительности за счет совершенствования микроэлектронной технологии можно оценить, опираясь на линейный прогноз снижения топологических норм производства элементной базы и отвечающий ему рост тактовой частоты (табл. 1.3).

| Факт | Линейный прогноз | |||||||||

|---|---|---|---|---|---|---|---|---|---|---|

| Год | 1980 | 1985 | 1990 | 1995 | 2000 | 2005 | 2010 | 2015 | 2020 | 2025 |

| Минимальный линейный размер (мкм) | 3-4 | 1-1,5 | (6-8) *10"' | (2,5-3) *10' | (1-2) *10-1 | (6-8) *102 | (3-4) *102 | (1,2-1,5) *102 | (6-7) *10_3 | (3-4) *10_3 |

| Тактовая частота | -10 МГц | -100 МГц | -250 МГц | -500 МГц | -1 ГГц | -3 ГГц | -5 ГГц | -10 ГГц | -50 ГГц | -100 ГГц |

| Темп роста | 25 раз | 10 раз | 10 раз | |||||||

| Фотолитография | Проекционая | Рентгеновская (мягкий рентген

|

||||||||

Приведенные значения потребной производительности говорят о том, что решить в реальном времени перечисленные выше задачи только за счет технологического совершенствования невозможно, так как достижение терагерцовых частот работы процессоров при комнатной температуре остается проблематичным даже в нанометровой области, в которую микроэлектроника способна перейти только в 2015-2020 гг.

Отсюда встает необходимость комплексного использования возможностей технологического и архитектурного развития вычислительных систем (ВС), чтобы они оказались способными решить экстремальные задачи с требуемым качеством по точности, достоверности и времени запаздывания в ВС.

Предельные возможности комплексного увеличения физической производительности ВС как за счет роста тактовой частоты, так и за счет совершенствования архитектуры можно оценить следующими соотношениями:

|

( 1.2) |

где:

-

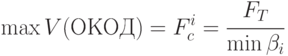

- максимальная (физическая) производительность однопроцессорных ЭВМ с одиночным потоком команд и одиночным потоком данных (ОКОД - рис. 1.10);

- максимальная (физическая) производительность однопроцессорных ЭВМ с одиночным потоком команд и одиночным потоком данных (ОКОД - рис. 1.10); -

- частота исполнения

- частота исполнения  -й ассемблерной инструкции, которая в современных RISC-процессорах постоянна (

-й ассемблерной инструкции, которая в современных RISC-процессорах постоянна (  ) и составляет 1-2 такта;

) и составляет 1-2 такта; -

- тактовая частота работы процессора;

- тактовая частота работы процессора;

|

( 1.3) |

где  - максимальная производительность параллельной архитектуры с одиночным потоком команд и множественным потоком данных (

- максимальная производительность параллельной архитектуры с одиночным потоком команд и множественным потоком данных (  - рис. 1.11), а

- рис. 1.11), а  - количество операндов в циклически обрабатываемом потоке данных с

- количество операндов в циклически обрабатываемом потоке данных с  ;

;

|

( 1.4) |

где  - "критический" путь программы обработки, определяемый количеством физически исполненных инструкций ассемблерного уровня (в дальнейшем слов-инструкций) в параллельной архитектуре с множественным потоком команд и множественным потоком данных (МКМД - рис. 1.12).

- "критический" путь программы обработки, определяемый количеством физически исполненных инструкций ассемблерного уровня (в дальнейшем слов-инструкций) в параллельной архитектуре с множественным потоком команд и множественным потоком данных (МКМД - рис. 1.12).

Соотношение (1.2) исходит из того, что в однопроцессорной системе ОКОД-типа предельная (физическая) производительность не может быть выше частоты исполнения ассемблерной слов-инструкции, которая зависит как от технологического уровня производства средств вычислительной техники (  ), так и от количества тактов

), так и от количества тактов  , затрачиваемых на исполнение

, затрачиваемых на исполнение  -й ассемблерной слов-инструкции. В свою очередь, коэффициент

-й ассемблерной слов-инструкции. В свою очередь, коэффициент  зависит от архитектуры однопроцессорной ЭВМ, аппаратные ресурсы которой расходуются на исполнение не только основных арифметико-логических, но и вспомогательных функций управления потоками команд и данных в ходе вычислительного процесса. Современные процессоры общего назначения и цифровые процессоры обработки сигналов и изображений как за рубежом, так и в России строятся по RISC- архитектуре, в которой сокращенная (редуцированная) система ассемблерных команд выбрана исходя из мини

мума системных аппаратно-временных издержек на управление вычислительным процессом и требования

зависит от архитектуры однопроцессорной ЭВМ, аппаратные ресурсы которой расходуются на исполнение не только основных арифметико-логических, но и вспомогательных функций управления потоками команд и данных в ходе вычислительного процесса. Современные процессоры общего назначения и цифровые процессоры обработки сигналов и изображений как за рубежом, так и в России строятся по RISC- архитектуре, в которой сокращенная (редуцированная) система ассемблерных команд выбрана исходя из мини

мума системных аппаратно-временных издержек на управление вычислительным процессом и требования  для всех основных и вспомогательных функций процессора. Это увеличивает длину программы обработки и количество обращений к памяти по отношению к CISC- архитектуре, но упрощает процесс управления многопроцессорным коллективом "равно-скоростных" вычислителей. ( CISC - архитектура с расширенной системой команд, каждая из которых исполняется со своим циклом.)

для всех основных и вспомогательных функций процессора. Это увеличивает длину программы обработки и количество обращений к памяти по отношению к CISC- архитектуре, но упрощает процесс управления многопроцессорным коллективом "равно-скоростных" вычислителей. ( CISC - архитектура с расширенной системой команд, каждая из которых исполняется со своим циклом.)

Соотношение (1.3) исходит из того, что в параллельных архитектурах ОКМД-типа максимальный коэффициент распараллеливания вычислений не может быть больше количества операндов  в циклически обрабатываемом потоке данных. Чтобы осуществить такое распараллеливание вычислений, необходимо в архитектуре ВС ОКМД-типа удвоить объем ОЗУ для буферизации циклически обрабатываемых потоков данных и увеличить число портов ввода-вывода данных до величины

в циклически обрабатываемом потоке данных. Чтобы осуществить такое распараллеливание вычислений, необходимо в архитектуре ВС ОКМД-типа удвоить объем ОЗУ для буферизации циклически обрабатываемых потоков данных и увеличить число портов ввода-вывода данных до величины  . Буферизация обеспечивает совмещение во времени процесса обработки потока данных, накопленного в предшествующем цикле, с процессом накопления потока данных для последующего цикла обработки, а увеличение портов ввода-вывода обеспечивает параллельную работу всех

. Буферизация обеспечивает совмещение во времени процесса обработки потока данных, накопленного в предшествующем цикле, с процессом накопления потока данных для последующего цикла обработки, а увеличение портов ввода-вывода обеспечивает параллельную работу всех  операционных устройств.

операционных устройств.

Соотношение (1.4) исходит из того, что в параллельных архитектурах МКМД-типа максимальный коэффициент распараллеливания по потоку команд не может превышать "длину"  реализуемой в реальном времени программы циклической обработки потока данных из

реализуемой в реальном времени программы циклической обработки потока данных из  операндов. При этом распараллеливание по потоку команд можно провести как по векторной, так и по конвейерной схеме. В первом случае все или часть команд программы исполняются одновременно и независимо друг от друга на разных операционных устройствах ВС, что возможно при полном отсутствии или малом количестве слабоинтенсивных информационных связей между фрагментами программы. Во втором случае все информационно связанные фрагменты программы исполняются на операционных устройствах, образующих конвейер с фиксированной структурой связей и фиксированным протоколом обмена информацией между двумя ближайшими соседями.

операндов. При этом распараллеливание по потоку команд можно провести как по векторной, так и по конвейерной схеме. В первом случае все или часть команд программы исполняются одновременно и независимо друг от друга на разных операционных устройствах ВС, что возможно при полном отсутствии или малом количестве слабоинтенсивных информационных связей между фрагментами программы. Во втором случае все информационно связанные фрагменты программы исполняются на операционных устройствах, образующих конвейер с фиксированной структурой связей и фиксированным протоколом обмена информацией между двумя ближайшими соседями.

В ВС реального времени максимальная "длина"  программы обработки лимитируется различными факторами, которые зависят от ее архитектуры.

программы обработки лимитируется различными факторами, которые зависят от ее архитектуры.

В ОКОД-архитектурах максимальная длина реализуемой в темпе реального времени программы обработки не может превышать количества физически исполненных ассемблерных слов-инструкций, которое косвенно характеризует "сложность" решаемой задачи и задается соотношением:

|

( 1.5) |

где  - цикл исполнения ассемблерной слов-инструкции.

- цикл исполнения ассемблерной слов-инструкции.

Соотношение (1.5) исходит из того, что в однопроцессорных ЭВМ реального времени программа должна завершить полный цикл обработки предыдущего отсчета до момента поступления последующего отсчета обрабатываемого сигнала. Нарушение этого условия приводит к потере входной и, как следствие, выходной информации, что может нарушить алгоритм решения задачи и привести к потере управления летательным аппаратом и его вооружением.

В ОКМД-архитектурах максимальная длина реализуемой в темпе реального времени программы обработки уже лимитируется временем формирования циклически обрабатываемой выборки входного сигнала из  операндов

операндов  :

:

|

( 1.6) |

Из соотношений (1.5) и (1.6) видно, что в ОКОД- и ОКМД-архитектурах от времени дискретизации по Котельникову зависит не только предельная производительность ВС, но и "сложность" решаемой ею в реальном времени задачи.

В МКМД-архитектурах максимальная длина реализуемой в темпе реального времени программы обработки уже не связана с ограничениями теоремы Котельникова и лимитируется допустимым временем (  ) задержки в ВС:

) задержки в ВС:

|

( 1.7) |

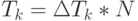

Подставив в (1.4) соотношение (1.7), получим:

|

( 1.8) |

где

Из (1.8) видно, что (максимальный) коэффициент распараллеливания вычислений по потокам команд и данных зависит от параметров решаемой задачи: периода дискретизации по Котельникову (  ), количе-ства операндов в циклически обрабатываемом потоке данных (

), количе-ства операндов в циклически обрабатываемом потоке данных (  ) и допустимого времени задержки в ВС (

) и допустимого времени задержки в ВС (  ). Это говорит о том, что параллельные архитектуры наиболее эффективны в проблемно-ориентированных областях их применения, для которых характерно априорное знание алгоритмов решения задач и их параметров.

). Это говорит о том, что параллельные архитектуры наиболее эффективны в проблемно-ориентированных областях их применения, для которых характерно априорное знание алгоритмов решения задач и их параметров.

Для большинства задач управления и боевого применения летательного аппарата  . Это объясняется тем, что для снижения влияния всевозможных помех и повышения достоверности вычислений требуется, как правило, усреднить полученные результаты по

. Это объясняется тем, что для снижения влияния всевозможных помех и повышения достоверности вычислений требуется, как правило, усреднить полученные результаты по  циклам обработки входного сигнала.

циклам обработки входного сигнала.

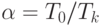

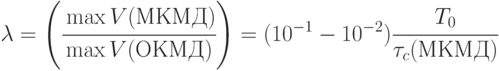

Сравнив (1.3) и (1.8), получим:

|

( 1.9) |

Производители ВС для армий США и НАТО в основном используют ОКМД-архитектуры, которые проще для проектирования, производства и эксплуатации. При этом они имеют более чем десятикратное превосходство перед отечественными производителями в частоте исполнения команд. Отечественные летательные аппараты по летно-техническим и боевым характеристикам не уступают зарубежным. Однако для полного использования этих возможностей требуется не уступающая лучшим зарубежным образцам авионика, в боевую эффективность и тактико-технические характеристики которой существенный вклад характеристики ВС, первое место среди которых занимают пропускная способность по потокам команд и данных, точность вычислений и отказоустойчивость.

Традиционно отечественная микроэлектроника, а с ней и вычислительная техника отстают от зарубежной на 1-2 поколения, что приводит к разнице в 1-2 порядка по частоте работы процессоров.

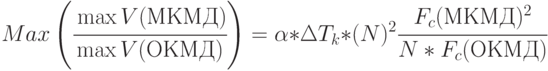

Из (1.9) видно, что для компенсации такого технологического отставания необходимо в отечественных ВС максимально задействовать МКМД-факторы распараллеливания вычислений. В таких условиях (1.9) принимает вид:

|

( 1.10) |

где  .

.

Из соотношения (1.10) следует, что выигрыш ВС с МКМД-архитектурой наступает при  , для чего необходимо выполнить достаточно слабое с технических позиций неравенство:

, для чего необходимо выполнить достаточно слабое с технических позиций неравенство:  .

.

Это неравенство требует, чтобы допустимое время задержки в ВС на один или два порядка превосходило время цикла исполнения ассемблерной слов-инструкции.

В частности, при  нс (что соответствует

нс (что соответствует  МГц) допустимое время задержки в ВС должно быть больше 10-5 с, что выполнимо для достаточно широкого круга задач управления летательным аппаратом и его вооружением.

МГц) допустимое время задержки в ВС должно быть больше 10-5 с, что выполнимо для достаточно широкого круга задач управления летательным аппаратом и его вооружением.

Сложность проектирования и эксплуатации ВС МКМД-типа намного превосходит аналогичные показатели для ВС ОКМД-типа, что требует создания нетрадиционных и эффективных инструментальных средств поддержки процессов проектирования и эксплуатации. Сложность задач разработки и сопровождения самих инструментальных средств превосходит сложность задач, которые решает большинство ВС МКМД-типа.

Это приводит к увеличению стоимости и сроков создания инструментальных платформ открытого типа, эффективную разработку которых невозможно осуществить без учета перспектив развития микроэлектроники и вычислительной техники в ближайшие 15-20 лет.